Patent application title: Layout Method for Mask, Semiconductor Device and Method for Manufacturing the Same

Inventors:

Sang Hee Lee (Eumseong-Gun, KR)

Gab Hwan Cho (Icheon-Si, KR)

IPC8 Class: AH01L310232FI

USPC Class:

257432

Class name: Electromagnetic or particle radiation light with optical element

Publication date: 2008-11-13

Patent application number: 20080277750

Inventors list |

Agents list |

Assignees list |

List by place |

Classification tree browser |

Top 100 Inventors |

Top 100 Agents |

Top 100 Assignees |

Usenet FAQ Index |

Documents |

Other FAQs |

Patent application title: Layout Method for Mask, Semiconductor Device and Method for Manufacturing the Same

Inventors:

SANG HEE LEE

Gab Hwan Cho

Agents:

SALIWANCHIK LLOYD & SALIWANCHIK;A PROFESSIONAL ASSOCIATION

Assignees:

Origin: GAINESVILLE, FL US

IPC8 Class: AH01L310232FI

USPC Class:

257432

Abstract:

A mask layout method, semiconductor device and method for fabricating the

same using a mask created according to the subject mask layout method are

provided. The semiconductor device can include a microlens main pattern

on a substrate and a microlens dummy pattern at a side of the microlens

main pattern. The microlens dummy pattern can be formed in plurality

using a mask created by the subject mask layout method. According to an

embodiment of the subject mask layout method, a microlens dummy pattern

can be created by forming a base dummy pattern and removing edge areas

from the base dummy pattern. The microlens dummy pattern can be created

to have a substantially circular shape. In one embodiment, the

substantially circular shape can be an octagon.Claims:

1. A semiconductor device comprising:a microlens main pattern on a

substrate; anda microlens dummy pattern on the substrate at a side of the

microlens main pattern.

2. The semiconductor device according to claim 1, further comprising a color filter dummy pattern provided on the substrate below the microlens dummy pattern.

3. The semiconductor device according to claim 1, wherein the microlens dummy pattern has a substantially circular shape.

4. The semiconductor device according to claim 3, wherein the microlens dummy pattern has an octagonal shape.

5. A method of manufacturing a semiconductor device, comprising:forming a microlens main pattern on a substrate; andforming a microlens dummy pattern on the substrate at a side of the microlens main pattern.

6. The method according to claim 5, further comprising forming a color filter dummy pattern before the forming of the microlens main pattern and the forming of the microlens dummy pattern.

7. The method according to claim 5, wherein the microlens dummy pattern is formed to have a substantially circular shape.

8. The method according to claim 7, wherein the microlens dummy pattern is formed to have an octagonal shape.

9. The method according to claim 5, wherein the forming of the microlens main pattern and the forming of the microlens dummy pattern are simultaneously performed.

10. The method according to claim 5, wherein the forming of the microlens main pattern and the forming of the microlens dummy pattern are performed in separate steps.

11. A layout method for a mask, comprising:forming a microlens main pattern in a main chip region; andforming a microlens dummy pattern in a region where the microlens main pattern is not formed.

12. The method according to claim 11, wherein forming the microlens dummy pattern comprises:forming a base dummy pattern in the region where the microlens main pattern is not formed; andremoving edge areas from the base dummy pattern to form the microlens dummy pattern.

13. The method according to claim 12, wherein the base dummy pattern is a polygonal shape.

14. The method according to claim 13, wherein the base dummy pattern is a regular square shape.

15. The method according to claim 12, wherein removing the edge areas from the base dummy pattern comprises:defining the edge areas of the base dummy pattern; andremoving the edge areas from the base dummy pattern using a software layout tool.

16. The method according to claim 15, wherein the edge areas have right-angled isosceles triangular shapes.

17. The method according to claim 16, wherein lateral sides of the right-angled isosceles triangle, except for its hypotenuse, have a length which corresponds to 1/3 length of one lateral side of the base dummy pattern.

Description:

CROSS-REFERENCE TO RELATED APPLICATION

[0001]The present application claims the benefit under 35 U.S.C. §119 of Korean Patent Application No. 10-2007-0045624, filed May 10, 2007, which is hereby incorporated by reference in its entirety.

BACKGROUND

[0002]In general, a semiconductor device has a multi-layer structure, in which each layer of the multi-layer structure is generally formed through a deposition process or a sputtering process, and then patterned through a lithography process.

[0003]However, various problems may occur due to differences in size and density of patterns formed on a substrate of the semiconductor device. To solve the above problems, methods of forming a dummy pattern together with a main pattern are being developed.

BRIEF SUMMARY

[0004]Embodiments of the present invention provide a layout method for a mask, and a semiconductor device and method for manufacturing the same utilizing a mask formed according to the subject mask layout method.

[0005]An embodiment of the mask layout method provides a microlens dummy pattern.

[0006]According to embodiments of the subject mask layout method pattern uniformity can be ensured.

[0007]A mask layout method according to an embodiment of the present invention is capable of enhancing pattern density.

[0008]In addition, a mask layout method according to an embodiment of the present invention is capable of simplifying designing and manufacturing processes.

[0009]A semiconductor device according to an embodiment can include a microlens main pattern on a substrate, and a microlens dummy pattern on the substrate near a side of the microlens main pattern.

[0010]In addition, a method of manufacturing a semiconductor device according to an embodiment can include forming a microlens main pattern on a substrate, and forming a microlens dummy pattern at a side of the microlens main pattern.

[0011]Further, a layout method for a mask according to an embodiment includes forming a microlens main pattern in a main chip region, and forming a microlens dummy pattern in a region where the microlens main pattern is not formed.

BRIEF DESCRIPTION OF THE DRAWINGS

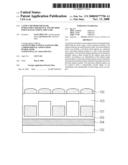

[0012]FIG. 1 is a plan view of a semiconductor device according to an embodiment.

[0013]FIG. 2 is a cross-sectional view of a semiconductor device taken along line I-I' of FIG. 1 according to an embodiment.

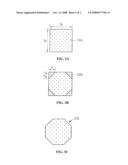

[0014]FIGS. 3A to 3C are schematic views for describing a layout method of a mask according to an embodiment.

DETAILED DESCRIPTION

[0015]Hereinafter, a layout method for a mask, a semiconductor device, and a method for manufacturing the same according to embodiments of the present invention will be described with reference to accompanying drawings.

[0016]In the description of embodiments, it will be understood that when a layer (or film) is referred to as being `on` another layer or substrate, it can be directly on another layer or substrate, or intervening layers may also be present. Further, it will be understood that when a layer is referred to as being `under` another layer, it can be directly under another layer, or one or more intervening layers may also be present. In addition, it will also be understood that when a layer is referred to as being `between` two layers, it can be the only layer between the two layers, or one or more intervening layers may also be present.

[0017]Referring to FIGS. 1 and 2, a semiconductor device according to an embodiment can include a microlens main pattern (not shown) formed on a substrate 100 of the semiconductor device, and a microlens dummy pattern 102 formed at a side of the microlens main pattern.

[0018]According to an embodiment, the microlens dummy pattern 102 is provided in a region where the microlens main pattern is not formed, so that pattern uniformity can be improved between a main pattern region and a dummy pattern region.

[0019]In addition, according to an embodiment, the microlens dummy pattern 102 can be formed to have a substantially circular shape. The substantially circular shape can be used to improve pattern uniformity between the main pattern region and the dummy pattern region. In one embodiment, the substantially circular shape of the microlens dummy pattern 102 can be an octagonal structure.

[0020]Although the microlens dummy pattern 102 is shown in the figures having the octagonal shape, this is for illustrative purposes only. The microlens dummy pattern 102 can be formed in a variety of shapes.

[0021]Hereinafter, a method of manufacturing the semiconductor device according to an embodiment will be described with reference to FIGS. 1 and 2.

[0022]A substrate 100 can be provided with various structures (not shown) according to a design, and a metal pattern 104 can be formed on the substrate 100. The metal pattern 104 can be the uppermost metal pattern, but embodiments are not limited thereto.

[0023]Next, an interlayer dielectric layer 105 can formed on the substrate 100 having the metal pattern 104. The interlayer dielectric layer 105 can have a single layer structure or a multi-layer structure.

[0024]Then, in certain embodiments, a color filter layer can be formed on the interlayer dielectric layer 105. The color filter layer can include a color filter main pattern (not shown) and a color filter dummy pattern 101. In one embodiment having a color filter layer, the color filter main pattern can include a red-green-blue (RGB) color filter main pattern formed by coating and patterning dyeable resist to filter light according to wavelengths of the light.

[0025]The RGB color filter main pattern includes red (R), green (G) and blue (B) color filters, which can be formed by selectively performing photolithography processes three times relative to red (R), green (G) and blue (B) color layers.

[0026]After forming the red (R), green (G) and blue (B) color filters, a UV exposure process can be performed to improve stability of the color filter layer surface.

[0027]Then, a planarization layer 103 can be formed on the color filter layer including the color filter main pattern and the color filter dummy pattern 101.

[0028]In an embodiment, the planarization layer 103 can be formed on the color filter main pattern to prepare the substrate for a microlens layer formed on the planarization layer 103 and to adjust the focal length.

[0029]In certain embodiments, a heat-treatment process can be performed to cure the planarization layer 103. In one embodiment, the heat-treatment process is performed at the temperature of about 150° C. to 300° C. to cure and stabilize the planarization layer 103.

[0030]Then a microlens main pattern (not shown) and a microlens dummy pattern 102 can be formed on the planarization layer 103. In one embodiment, the microlens main pattern and the microlens dummy pattern 102 can be formed sequentially using separate masks. In another embodiment, the microlens main pattern and the microlens dummy pattern 102 can be formed simultaneously.

[0031]According to embodiments of the present invention, the microlens dummy pattern 102 is inserted into a region where the microlens main pattern is not formed, so that pattern uniformity can be improved between a main pattern region and a dummy pattern region.

[0032]In addition, according to an embodiment, the microlens dummy pattern 102 has a substantially circular shape, so that pattern uniformity can be improved between the main pattern region and the dummy pattern region. In a specific embodiment, the substantially circular shape of the microlens dummy pattern 102 can include an octagonal structure. Of course, embodiments are not limited to the octagonal structure.

[0033]Hereinafter, a layout method for a mask according to an embodiment of the present invention will be described with reference to FIGS. 3A to 3C. A microlens main pattern (not shown) can be created on a main chip region (not shown) during a layout design with, for example, a layout software tool.

[0034]Then, a microlens dummy pattern 102 can be formed on a region where the microlens main pattern is not formed using the layout software tool.

[0035]First, referring FIG. 3A, according to one embodiment, a base dummy pattern 102a having a polygonal shape can be formed on a region where the microlens main pattern is not formed. The base dummy pattern 102a can have a regular polygonal shape. In a specific embodiment, the base dummy pattern 102a has a regular square shape, but embodiments are not limited thereto.

[0036]Referring to FIG. 3B, edge areas 102b can be defined at edges of the base dummy pattern 102a.

[0037]In one embodiment, the edge areas 102b can have right-angled isosceles triangular shapes, but embodiments are not limited thereto.

[0038]In a specific embodiment using light-angled isosceles triangular shapes, the lateral sides of the right-angled isosceles triangle, except for its hypotenuse, can have a length (a) corresponding to 1/3 of the length (3a) of one lateral side of the base dummy pattern 102a.

[0039]Then, referring to FIG. 3C, the edge areas 102b can be removed from the base dummy pattern 102a to form the microlens dummy pattern 102. Any known layout software tool can be used to accomplish this step.

[0040]As described above, according to an embodiment, the microlens dummy pattern having a substantially circular shape can be formed by using a base dummy pattern having a regular square shape, so that layout of the dummy pattern can be achieved with high speed and improved accuracy.

[0041]In addition, according to embodiments, the microlens dummy pattern is inserted into a region where the microlens main pattern is not formed, so that pattern uniformity can be improved between a main pattern region and a dummy pattern region.

[0042]Further, according to an embodiment, the microlens dummy pattern can be produced by simply removing edge regions of a regular square shape, so that data load required for the layout of the dummy pattern can be reduced.

[0043]According to an embodiment, each pattern can have a uniform CD (critical dimension) due to the uniformity of the pattern.

[0044]Further, according to an embodiment the layout process and the manufacturing process can be simplified.

[0045]Any reference in this specification to "one embodiment," "an embodiment," "example embodiment," etc., means that a particular feature, structure, or characteristic described in connection with the embodiment is included in at least one embodiment of the invention. The appearances of such phrases in various places in the specification are not necessarily all referring to the same embodiment. Further, when a particular feature, structure, or characteristic is described in connection with any embodiment, it is submitted that it is within the purview of one skilled in the art to effect such feature, structure, or characteristic in connection with other ones of the embodiments.

[0046]Although embodiments have been described with reference to a number of illustrative embodiments thereof, it should be understood that numerous other modifications and embodiments can be devised by those skilled in the art that will fall within the spirit and scope of the principles of this disclosure. More particularly, various variations and modifications are possible in the component parts and/or arrangements of the subject combination arrangement within the scope of the disclosure, the drawings and the appended claims. In addition to variations and modifications in the component parts and/or arrangements, alternative uses will also be apparent to those skilled in the art.

User Contributions:

comments("1"); ?> comment_form("1"); ?>Inventors list |

Agents list |

Assignees list |

List by place |

Classification tree browser |

Top 100 Inventors |

Top 100 Agents |

Top 100 Assignees |

Usenet FAQ Index |

Documents |

Other FAQs |

User Contributions:

Comment about this patent or add new information about this topic:

| People who visited this patent also read: | |

| Patent application number | Title |

|---|---|

| 20150070818 | INKJET INK, PRINTING METHOD, AND CERAMIC ELECTRONIC COMPONENT |

| 20150070817 | MULTI-LAYER CERAMIC CAPACITOR AND METHOD OF MANUFACTURING THE SAME |

| 20150070816 | CAPACITOR FABRICATION USING NANO MATERIALS |

| 20150070815 | ELECTROSTATIC CHUCK MEMBER |

| 20150070814 | ELECTROSTATIC CHUCK WITH VARIABLE PIXILATED HEATING |