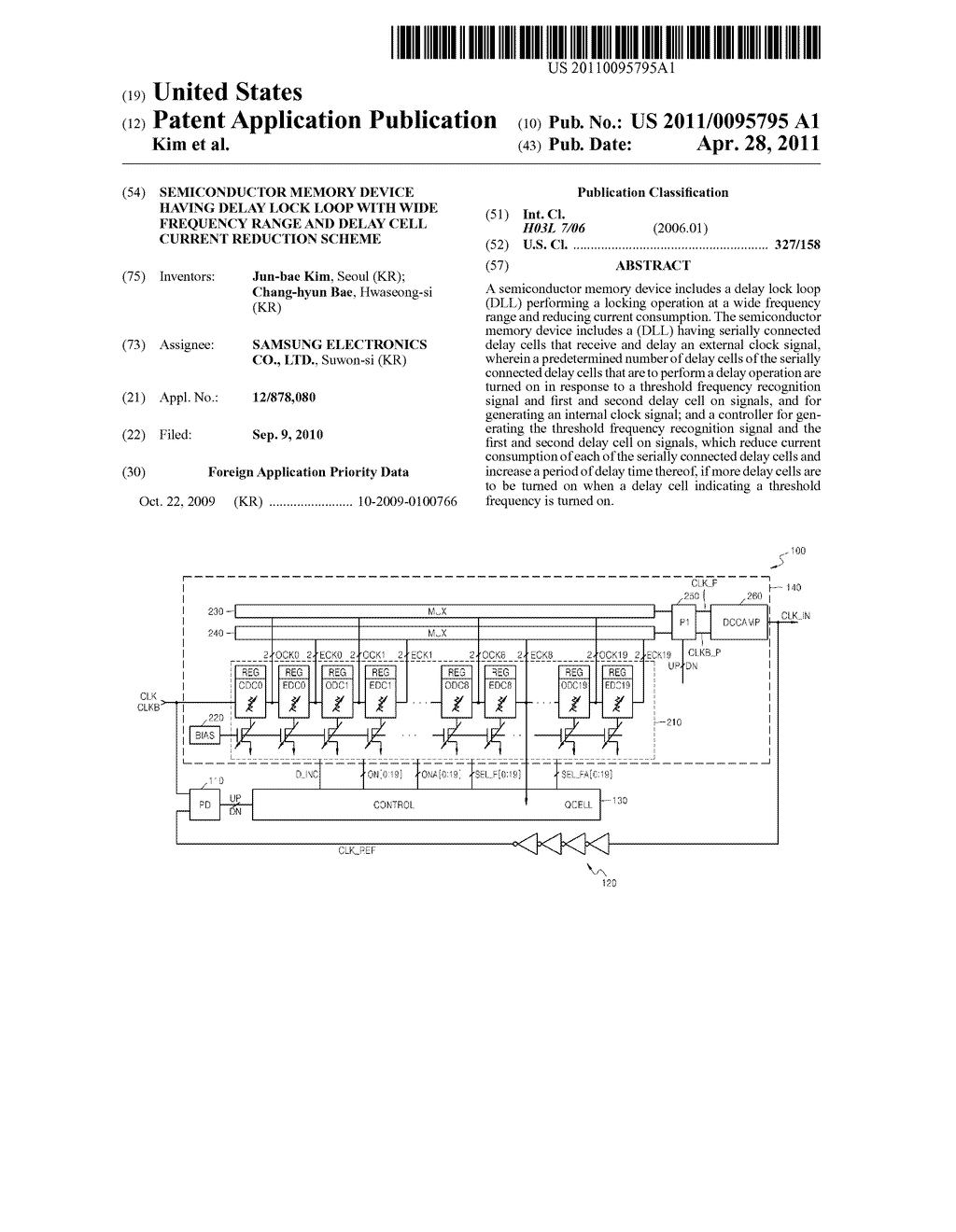

SEMICONDUCTOR MEMORY DEVICE HAVING DELAY LOCK LOOP WITH WIDE FREQUENCY RANGE AND DELAY CELL CURRENT REDUCTION SCHEME - diagram, schematic, and image 01

Back to SEMICONDUCTOR MEMORY DEVICE HAVING DELAY LOCK LOOP WITH WIDE FREQUENCY RANGE AND DELAY CELL CURRENT REDUCTION SCHEME , All Patents .