Patent application title: INSULATION STRUCTURE FOR HIGH TEMPERATURE CONDITIONS AND MANUFACTURING METHOD THEREOF

Inventors:

Young Ki Lee (Seoul, KR)

Seog Moon Choi (Seoul, KR)

Sang Hyun Shin (Hwasung, KR)

Assignees:

Samsung Electro-Mechanics Co., Ltd.

IPC8 Class:

USPC Class:

257 98

Class name: Active solid-state devices (e.g., transistors, solid-state diodes) incoherent light emitter structure with reflector, opaque mask, or optical element (e.g., lens, optical fiber, index of refraction matching layer, luminescent material layer, filter) integral with device or device enclosure or package

Publication date: 2011-10-27

Patent application number: 20110260198

Abstract:

An insulation structure for high temperature conditions and a

manufacturing method thereof. In the insulation structure, a substrate

has a conductive pattern formed on at least one surface thereof for

electrical connection of a device.

A metal oxide layer pattern is formed on a predetermined portion of the

conductive pattern by anodization, the metal oxide layer pattern made of

one selected from a group consisting of Al, Ti and Mg.Claims:

1. An insulation structure for high temperature conditions comprising: a

substrate having a conductive pattern formed on at least one surface

thereof for electrical connection of a device; and a metal oxide layer

pattern formed on a predetermined portion of the conductive pattern by

anodization, the metal oxide layer pattern comprising one selected from a

group consisting of Al, Ti and Mg.

2. The insulation structure according to claim 1, wherein the device comprises a power chip or a light emitting diode.

3. The insulation structure according to claim 1, further comprising an upper substrate provided on the metal oxide layer pattern.

4. The insulation structure according to claim 3, wherein the upper substrate and the metal oxide pattern are bonded together by Au/Sn eutectic bonding.

5. The insulation structure according to claim 3, wherein the device comprises a light emitting diode, and the upper substrate comprises a reflecting plate.

6. The insulation structure according to claim 1, wherein the substrate is a Si substrate.

7-11. (canceled)

Description:

CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a Divisional of U.S. application Ser. No. 11/723,236, filed on Mar. 19, 2007, which claims the benefit of Korean Patent Application No. 2006-25454 filed on Mar. 20, 2006 in the Korean Intellectual Property Office, the disclosure of each of which is incorporated herein by reference.

BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] The present invention relates to an insulation structure for high temperature conditions and a manufacturing method thereof, and more particularly, to an insulation structure in which a metal oxide in place of a conventional epoxy resin is employed as an insulation layer through anodization, thereby suitable for subsequent high temperature conditions, and a manufacturing method thereof.

[0004] 2. Description of the Related Art

[0005] Various substrates or packages for current use are bonded to another substrate or package by employing solder paste, conductive paste or thermal eutectic method. Here, an electrical insulating layer (solder resist or insulation film) is formed on a conductive material to prevent the paste or conductive material from being electrically connected to other conductive parts.

[0006] Conventionally, in order to electrically insulate the substrate or package, a solder resist is formed through a liquid epoxy resin or film which responds to light. FIG. 1 illustrates a conventional process of forming such a solder resist. As shown in FIG. 1, conventionally, a resin 5 for forming a solder resist is applied on both surfaces of a substrate 1 each having a predetermined pattern 3. Then, the resin 5 is exposed, developed and cured to form a desired solder resist pattern.

[0007] But the solder resist as an insulating material is thermally weak. Thus, in high temperature conditions necessary for manufacturing the package these days, the solder resist suffers delamination due to thermal transformation, thereby undermining reliability of the substrate. Also, a general epoxy material exhibits high heat resistance, thus inadequate for dissipating heat from a device.

SUMMARY OF THE INVENTION

[0008] The present invention has been made to solve the foregoing problems of the prior art and therefore an aspect of the present invention is to provide an insulation structure in which an adodizable metal such as Al is deposited by PVD for electrical insulation and transformed into a non-conductive material through anodization to be employed as an insulation layer, thereby overcoming conventional problems associated with high temperature conditions, and a manufacturing method thereof.

[0009] According to an aspect of the invention, the insulation structure for high temperature conditions includes a substrate having a conductive pattern formed on at least one surface thereof for electrical connection of a device; and a metal oxide layer pattern formed on a predetermined portion of the conductive pattern by anodization, the metal oxide layer pattern comprising one selected from a group consisting of Al, Ti and Mg.

[0010] According to another aspect of the invention, the method for manufacturing the insulation structure for high temperature conditions includes:

[0011] preparing a substrate having a conductive pattern formed on at least one surface thereof for electrical connection of a device;

[0012] depositing a metal selected from a group consisting of Al, Ti and Mg on the substrate with the conductive pattern formed thereon by PVD to form a metal deposition layer;

[0013] oxidizing the metal deposition layer by anodization to form a metal oxide layer;

[0014] applying a photosensitive film on the metal oxide layer, and exposing and developing the photosensitive film to form a plurality of photosensitive film patterns and exposing the metal oxide layer between the plurality of the photosensitive film patterns; and

[0015] removing the metal oxide layer exposed between the plurality of the photosensitive film patterns by etching a surface of the substrate using the photosensitive film pattern as a mask, thereby forming a metal oxide layer pattern on the entirety of, or in part of, the conductive pattern.

BRIEF DESCRIPTION OF THE DRAWINGS

[0016] The above and other objects, features and other advantages of the present invention will be more clearly understood from the following detailed description taken in conjunction with the accompanying drawings, in which:

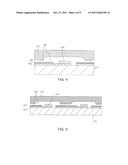

[0017] FIG. 1 illustrates a conventional method for manufacturing an insulation structure which adopts a solder resist as an insulating layer;

[0018] FIG. 2 is a schematic view illustrating an insulation structure according to an embodiment of the invention;

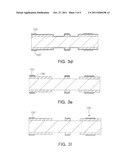

[0019] FIGS. 3a to 3f illustrate a method for manufacturing an insulation structure according to another embodiment of the invention;

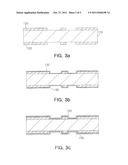

[0020] FIG. 4 is a schematic view illustrating an electrical connection of devices in a wafer level package (WLP) process using the insulation structure of the invention;

[0021] FIG. 5 illustrates a successive arrangement of those structures as shown in FIG. 4; and

[0022] FIG. 6 is a schematic view illustrating a successive arrangement of an electrical connection of LEDs using the insulation structure of the invention.

DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

[0023] Exemplary embodiments of the present invention will now be described in detail with reference to the accompanying drawings.

[0024] FIG. 2 is a schematic cross-sectional view illustrating an insulation structure according to an embodiment of the invention. As shown in FIG. 2, the insulation structure 10 includes a substrate 11 and a metal oxide layer pattern 15. The substrate 11 has conductive patterns formed on both surfaces thereof to electrically connect a device. The metal oxide layer pattern 15 is formed on a predetermined portion of the conductive pattern 13 by anodization and made of one selected from a group consisting of Al, Ti and Mg.

[0025] In this invention, the substrate 11 may have a conductive pattern formed on only one surface thereof, and the substrate of the invention is not limited to a particular kind. For example, the substrate 11 may be made of an epoxy resin or an oxide. Alternatively, the substrate 11 maybe an insulating layer of a general printed circuit board (PCB). Alternatively, the substrate 11 may be a metal substrate made of e.g., Si.

[0026] Moreover, in this invention, the conductive pattern 13 for electrically connecting the device denotes a metal pattern in use for electric connections in a substrate, a package or a similarly-functioning structure for general use. However, the metal of invention is not limited to a specific kind.

[0027] Preferably, the conductive pattern 13 is made of a metal selected from a group consisting of Al, Ag, Cu, Pt, Au and Ni. Also, according to the invention, preferably, the device is either a power chip or a light emitting diode (LED).

[0028] Furthermore, the insulation structure 10 of the invention has the metal oxide layer pattern 15, i.e., insulating layer formed on a predetermined portion of the conductive pattern by anodization. Here, preferably, one selected from a group consisting of Al, Ti and Mg is anodized to form the metal oxide layer 15.

[0029] What is more, the insulation structure of the invention may include an upper substrate provided on the metal oxide layer pattern 15. In a case where the device is a light emitting diode, the upper substrate is preferably configured as a reflector or a reflecting plate.

[0030] Preferably, the upper substrate and the oxide layer pattern 15 are bonded together by eutectic bonding. More preferably, the upper substrate and the oxide layer pattern 15 are bonded together by Au/Sn eutectic bonding.

[0031] Then, an explanation will be given about a method for manufacturing an insulation structure of the invention.

[0032] FIGS. 3a and 3f illustrate a method for manufacturing an insulation structure according to an embodiment of the invention.

[0033] As shown in 3(a), according to the invention, first, a substrate 110 with a conductive pattern 120 formed on at least one surface thereof is prepared to electrically connect a device. As described above, the substrate 110 of the invention is not limited to a particular kind, but all kinds of the substrate are adoptable as long as the conductive layer pattern can be formed on at least one surface thereof. Moreover, the conductive pattern 120 can be composed as described above. Also, according to the invention, preferably, the device is either a power chip or a light emitting diode.

[0034] Next, according to the invention, a metal selected from a group consisting of Al, Ti and Mg is deposited by PVD on the substrate with the conductive pattern 120 thereon to form a metal deposition layer. Such a metal is easily anodizable in a following process.

[0035] Meanwhile, the invention is not limited to a type of the PVD process and a specific process condition thereof. But preferably, the metal is deposited by sputtering or evaporation.

[0036] Subsequently, according to the invention, the metal deposition layer on the substrate is oxidized by general anodization, and thus transformed into a metal oxide layer 130 as shown in FIG. 3(b). In this fashion, the metal oxide layer 130 can be obtained by general anodization. That is, the substrate with the metal deposition layer formed thereon is immersed in an electrolytic bath and electrolytically reacted as an anode.

[0037] Then according to the invention, as shown in FIG. 3(c), a photosensitive film 150 is applied on the metal oxide layer 130, and exposed and developed to form a photosensitive film pattern 150' as shown in FIG. 3(d).

[0038] Afterwards, as shown in FIG. 3(e), a surface of the substrate with the photosensitive film pattern 150' thereon is etched to remove the metal oxide layer 130. According to the invention, the etching of the invention is exemplified by a general chemical etching but not limited thereto.

[0039] Next as shown in FIG. 3(f), the photosensitive film pattern 150' is removed to produce an insulation structure 100 with the metal oxide layer pattern 130' formed on a predetermined portion of the conductive pattern 120.

[0040] In addition, according to the invention, the insulation structure may include an upper substrate (not illustrated) attached onto the metal oxide layer pattern 130'. In a case where the device is alight emitting diode, the upper substrate is preferably configured as a reflecting plate.

[0041] Preferably, the upper substrate and the oxide layer pattern 130' are bonded together by eutectic bonding. More preferably, the upper substrate and the oxide layer pattern 130' are bonded together by Au/Sn eutectic bonding.

[0042] The insulation structure of the invention as described above ensures effective insulating characteristics when used to connect devices with one another in a high temperature Wafer Level Package (WLP) process. Also, the insulation structure of the invention effectively overcomes problems associated with conventional use of epoxy resin as an insulating layer.

[0043] The invention will be explained in detail by way of example.

EXAMPLE

[0044] A Si substrate with a copper conductive pattern formed on both surfaces thereof was prepared. Then Al was sputtered on the substrate to form an Al deposition layer. Thereafter, the Al deposition layer was transformed into an Al2O3 oxide layer using typical anodization, and a photosensitive film was applied on the oxide layer. Subsequently, the photosensitive film was exposed and developed to form a pattern and a surface of the Al2O3 oxide layer was etched to form an Al2O3 oxide layer pattern on the conductive pattern. Next, the upper substrate was bonded onto the Al2O3 oxide layer pattern, i.e., insulation layer by Au/Sn eutectic bonding in a high temperature WLP process.

[0045] FIG. 4 is a schematic view illustrating an electrical connection of a device using an insulation structure of the invention in a high temperature WLP process. As shown in FIG. 4, reference numeral 210 denotes a base wafer where the device is formed or mounted. Reference numeral 220 denotes a conductive pattern, reference numeral 230 denotes a device, reference numeral 250 denotes an Al2O3 oxide layer pattern, reference numeral 270 denotes an upper substrate (a wafer for the upper package), and reference numeral 290 denotes a bonding layer for eutectic bonding.

[0046] However, in case of bonding in this wafer level package process, the device is electrically connected through a layer which electrically insulates the bonding layer 290 from conductive lines. In this example, the Al2O3 oxide layer 250 is adopted for the insulation layer. This effectively eliminates problems, such as gas occurrence and thermal deformation, associated with eutectic bonding in the conventional WLP process where an epoxy layer is used as the insulation layer.

[0047] FIG. 5 illustrates a successive arrangement of those structures as shown in FIG. 4.

[0048] Meanwhile, FIG. 6 illustrates LEDs 310 mounted on the conductive pattern. Here, a reflecting plate 350 is eutectically bonded onto an Al2O3 oxide layer 330.

[0049] As set forth above, according to exemplary embodiments of the invention, a metal oxide layer is formed by anodization to be utilized as an insulation layer. This solves problems with conventional use of an epoxy insulation layer, i.e., limitations experienced during high temperature conditions or the formation of a microstructure pattern. Also, unlike the conventional method based on low temperature conditions, the invention enables high temperature conditions of at least 300quadrature and the insulation layer is sufficiently adjustable in its thickness in accordance with electrical properties. In addition, the metal oxide insulation layer formed by anodization is improved in heat transfer properties over the conventional one, thereby effectively dissipating heat from a heat generating device.

[0050] While the present invention has been shown and described in connection with the preferred embodiments, it will be apparent to those skilled in the art that modifications and variations can be made without departing from the spirit and scope of the invention as defined by the appended claims.

User Contributions:

Comment about this patent or add new information about this topic: